Microchip SY56016R Bedienungsanleitung

Microchip Nicht kategorisiert SY56016R

Lies die bedienungsanleitung für Microchip SY56016R (11 Seiten) kostenlos online; sie gehört zur Kategorie Nicht kategorisiert. Dieses Handbuch wurde von 29 Personen als hilfreich bewertet und erhielt im Schnitt 4.9 Sterne aus 3 Bewertungen. Hast du eine Frage zu Microchip SY56016R oder möchtest du andere Nutzer dieses Produkts befragen? Stelle eine Frage

Seite 1/11

SY56016R

Low Voltage 1.2V/1.8V/2.5V CML Differential

Line Driver/Receiver 6.4Gbps with Equalization

Precision Edge is a registered trademark of Micrel, Inc

MLF and MicroLeadFrame are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

December 2008

M9999-121708-A

[email protected] or (408) 955-1690

General Description

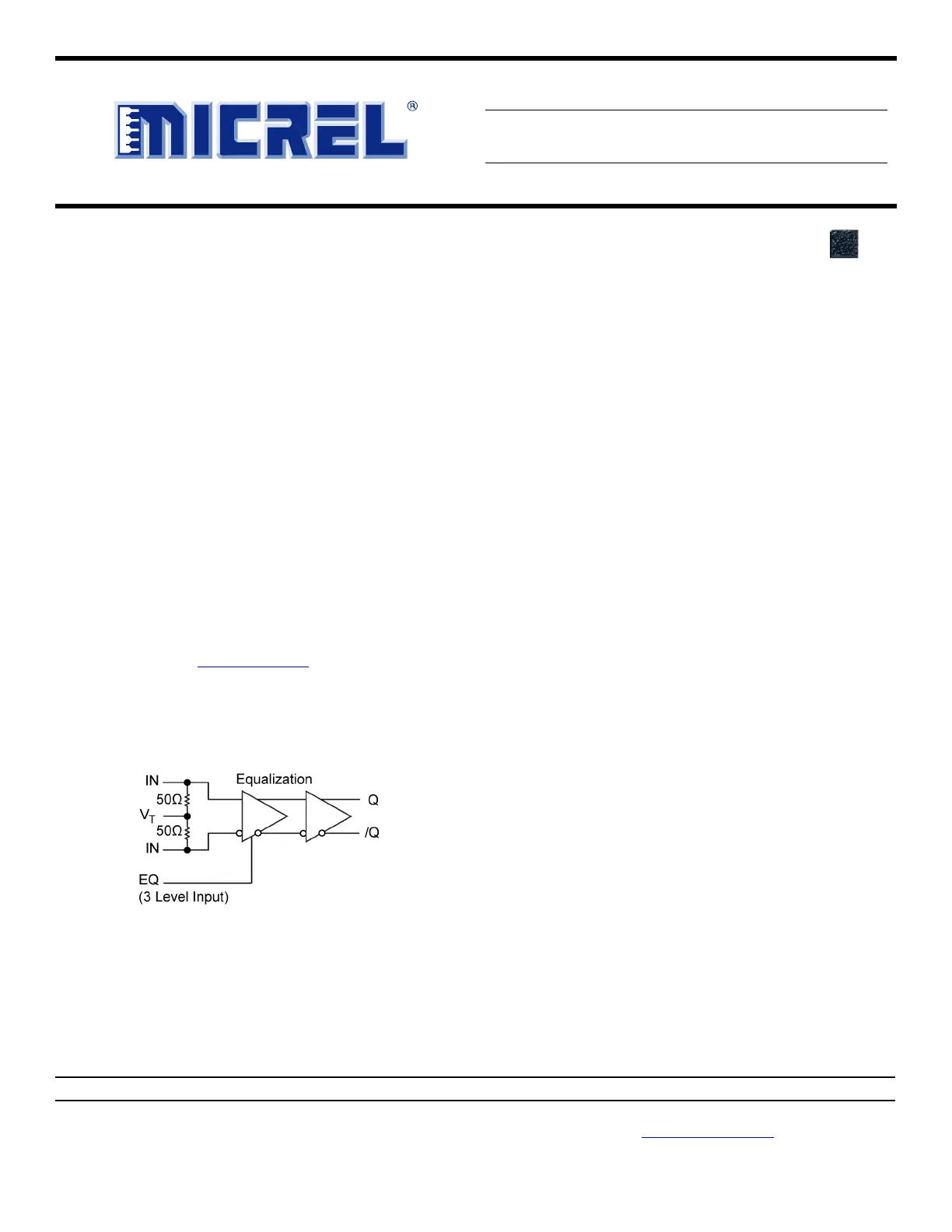

The SY56016R is a fully differential, low voltage

1.2V/1.8V/2.5V CML Line Driver/Receiver with input

equalization. The SY56016R can process clock signals as

fast as 5.0GHz or data patterns up to 6.4Gbps.

The differential input includes Micrel’s unique, 3-pin input

termination architecture that interfaces to CML differential

signals, without any level-shifting or termination resistor

networks in the signal path. The differential input can also

accept AC-coupled CML, LVPECL, and LVDS signals.

Input voltages as small as 200mV (400mV

PP

) are applied

before the 9”, 18” or 27” FR4 transmission line. For AC-

coupled input interface applications, an internal voltage

reference is provided to bias the V

T

pin. The outputs are

CML, with extremely fast rise/fall times guaranteed to be

less than 80ps.

The SY56016R operates from a 2.5V ±5% core supply and

a 1.2V, 1.8V or 2.5V ±5% output supply and is guaranteed

over the full industrial temperature range (–40°C to

+85°C). The SY56016R is part of Micrel’s high-speed,

Precision Edge

®

product line.

Datasheets and support documentation can be found on

Micrel’s web site at: www.micrel.com.

Functional Block Diagram

Precision Edge

®

Features

∑1.2V/1.8V/2.5V CML Differential Line Driver/Receiver

with Equalization

∑Equalizes 9, 18, 27 inches of FR4

∑Guaranteed AC performance over temperature and

voltage:

–DC-to >6.4Gbps Data throughput

–DC-to >5.0GHz Clock throughput

–<250ps propagation delay (IN-to-Q)

–<80ps rise/fall times

∑Ultra-low jitter design

–<1ps

RMS

random jitter

∑High-speed CML outputs

∑2.5V ±5% V

CC

, 1.2V/1.8V/2.5V ±5% V

CCO

power supply

operation

∑Industrial temperature range: –40°C to +85°C

∑Available in 10-pin (2mm x 2mm) MLF

®

package

Applications

∑Data Distribution:

∑SONET clock and data distribution

∑Fibre Channel clock and data distribution

∑Gigabit Ethernet clock and data distribution

Markets

∑Storage

∑Test and measurement

∑Enterprise networking equipment

∑High-end servers

∑Metro area network equipment

Produktspezifikationen

| Marke: | Microchip |

| Kategorie: | Nicht kategorisiert |

| Modell: | SY56016R |

Brauchst du Hilfe?

Wenn Sie Hilfe mit Microchip SY56016R benötigen, stellen Sie unten eine Frage und andere Benutzer werden Ihnen antworten

Bedienungsanleitung Nicht kategorisiert Microchip

30 Januar 2026

23 Januar 2026

23 Januar 2026

20 Januar 2026

19 Januar 2026

15 Januar 2026

14 Januar 2026

14 Januar 2026

3 Dezember 2025

2 Dezember 2025

Bedienungsanleitung Nicht kategorisiert

Neueste Bedienungsanleitung für -Kategorien-

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026