Microchip SY58021U Bedienungsanleitung

Microchip Nicht kategorisiert SY58021U

Lies die bedienungsanleitung für Microchip SY58021U (17 Seiten) kostenlos online; sie gehört zur Kategorie Nicht kategorisiert. Dieses Handbuch wurde von 17 Personen als hilfreich bewertet und erhielt im Schnitt 4.4 Sterne aus 7 Bewertungen. Hast du eine Frage zu Microchip SY58021U oder möchtest du andere Nutzer dieses Produkts befragen? Stelle eine Frage

Seite 1/17

2023 Microchip Technology Inc. and its subsidiariesDS20006822A-page 1

SY58021U

Features

•Precision 1:4 LVPECL Fanout Buffer

•Low Jitter Performance

-70fs

RMS

Phase Jitter (Typical)

•Accepts an Input Signal as Low as 100mV

•Unique Input Termination and VT Pin Accept

DC-Coupled and AC-Coupled Differential Inputs:

LVPECL, LVDS, and CML

•100K LVPECL-Compatible 800mV Swing Output

•Power Supply 2.5V ±5% and 3.3V ±10%

•–40°C to +85°C Temperature Range

•Available in 16-Lead, 3mm x 3mm VQFN

Package

Applications

•All SONET and GigE Clock Distribution

•Fibre Channel Clock and Data Distribution

•Backplane Distribution

•High-End, Low-Skew, Multiprocessor,

Synchronous Clock Distribution

General Description

The SY58021U is a 2.5V/3.3V precision, high-speed,

fully differential 1:4 LVPECL fanout buffer. Optimized to

provide four identical output copies with less than 15ps

output skew and only 70fs

RMS

phase jitter, the

SY58021U can process clock signals as fast as 4GHz.

The differential input includes Microchip’s unique, 3-pin

input termination architecture interfaces to differential

LVPECL, CML, and LVDS signals (AC- or DC-coupled)

as small as 100mV without any level-shifting or

termination resistor networks in the signal path. For

AC-coupled input interface applications, an on-board

output reference voltage (V

REFAC

) is provided to bias

the VT pin. The outputs are 100K LVPECL compatible,

with extremely fast rise/fall times guaranteed to 70ps.

The SY58021U operates from a 2.5V ±5% supply or

3.3V ±10% supply and is guaranteed over the full

industrial temperature range (–40°C to +85°C). For

applications that require faster rise/fall times, or greater

bandwidth, consider the SY58022U 1:4 fanout buffer

with 400mV LVPECL output swing, or the SY58020U

1:4 CML fanout buffer. The SY58021U is part of

Microchip’s high-speed, Precision Edge

®

product line.

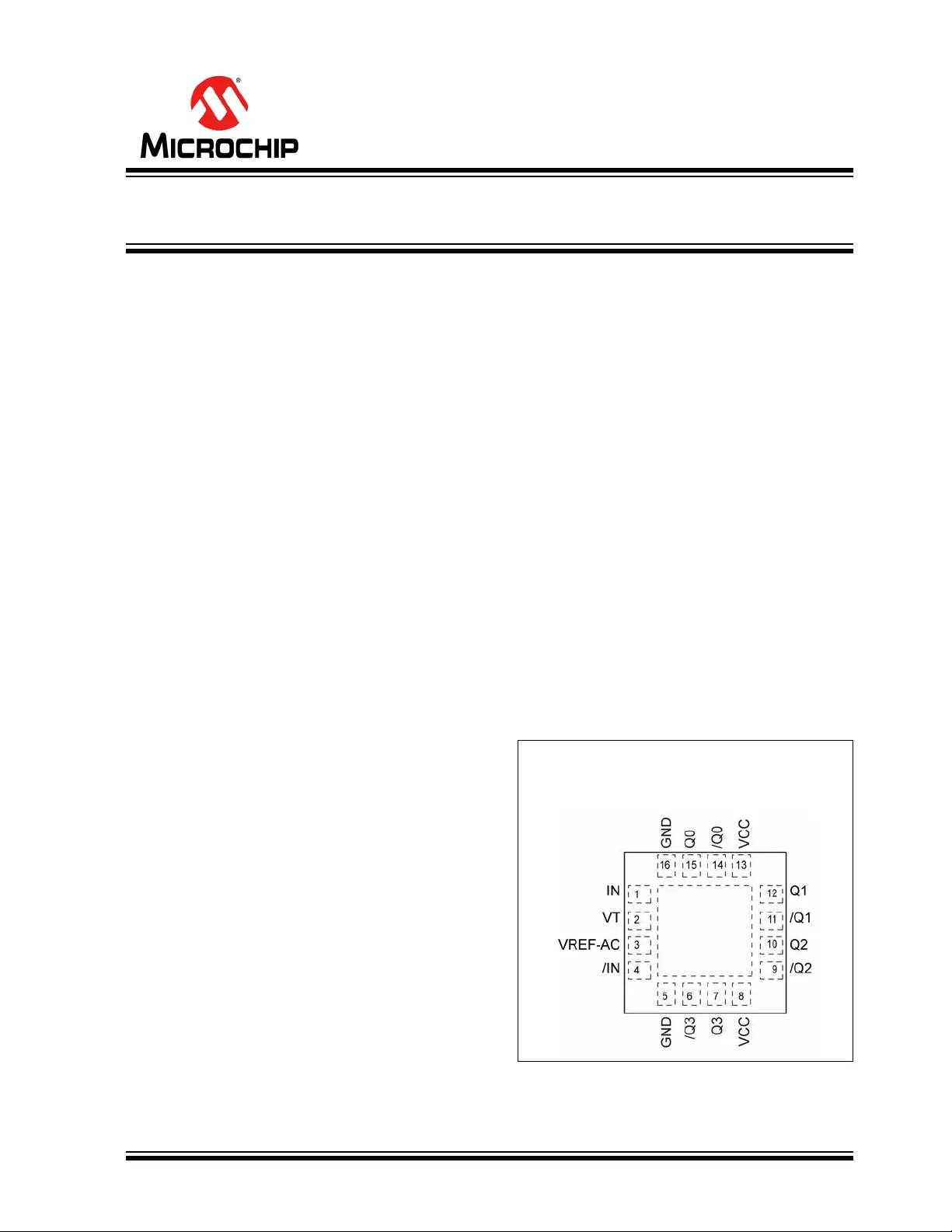

Package Type

SY58021U

16-Lead VQFN (M)

(Top View)

4GHz, 1:4 LVPECL Fanout Buffer/Translator

with Internal Termination

Produktspezifikationen

| Marke: | Microchip |

| Kategorie: | Nicht kategorisiert |

| Modell: | SY58021U |

Brauchst du Hilfe?

Wenn Sie Hilfe mit Microchip SY58021U benötigen, stellen Sie unten eine Frage und andere Benutzer werden Ihnen antworten

Bedienungsanleitung Nicht kategorisiert Microchip

30 Januar 2026

23 Januar 2026

23 Januar 2026

20 Januar 2026

19 Januar 2026

15 Januar 2026

14 Januar 2026

14 Januar 2026

3 Dezember 2025

2 Dezember 2025

Bedienungsanleitung Nicht kategorisiert

Neueste Bedienungsanleitung für -Kategorien-

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026