Texas Instruments LMK61E2 Bedienungsanleitung

Texas Instruments Nicht kategorisiert LMK61E2

Lies die bedienungsanleitung für Texas Instruments LMK61E2 (2 Seiten) kostenlos online; sie gehört zur Kategorie Nicht kategorisiert. Dieses Handbuch wurde von 2 Personen als hilfreich bewertet und erhielt im Schnitt 4.9 Sterne aus 9 Bewertungen. Hast du eine Frage zu Texas Instruments LMK61E2 oder möchtest du andere Nutzer dieses Produkts befragen? Stelle eine Frage

Seite 1/2

LMK61E2 Ultra-Low Jitter Programmable Oscillator With Internal EEPROM

1 Features

•Ultra-Low Noise, High Performance

–Jitter: 90fs RMS Typical f

OUT

> 100MHz

–PSRR: –70dBc, Robust Supply Noise Immunity

•Flexible Output Format; User Selectable

–LVPECL up to 1GHz

–LVDS up to 900MHz

–HCSL up to 400MHz

•Total Frequency Tolerance of ±50ppm

•System Level Features

–Frequency Margining: Fine and Coarse

–Internal EEPROM: User Configurable Default

Settings

•Other Features

–Device Control: I

2

C

–3.3V Operating Voltage

–Industrial Temperature Range (–40°C to +85°C)

–7mm × 5mm 8-Pin Package

–Create a Custom Design Using the LMK61E2

With the WEBENCH

®

Power Designer

2 Applications

•High-Performance Replacement for Crystal-,

SAW-, or Silicon-Based Oscillators

•Switches, Routers, Network Line Cards, Base

Band Units (BBU),Servers, Storage/SAN

•Test and Measurement

•Medical Imaging

•FPGA, Processor Attach

3 Description

The LMK61E2 device is an ultra-low jitter PLLatinum

™

programmable oscillator with a fractional-N frequency

synthesizer with integrated VCO that generates

commonly used reference clocks. The outputs can be

configured as LVPECL, LVDS, or HCSL.

The device features self start-up from on-chip

EEPROM that is factory programmed to generate

156.25MHz LVPECL output. The device registers

and EEPROM settings are fully programmable in-

system through I

2

C serial interface. Internal power

conditioning provide excellent power supply ripple

rejection (PSRR), reducing the cost and complexity of

the power delivery network. The device operates from

a single 3.3V ± 5% supply.

The device provides fine and coarse frequency

margining options through I

2

C serial interface to

support system design verification tests (DVT), such

as standard compliance and system timing margin

testing.

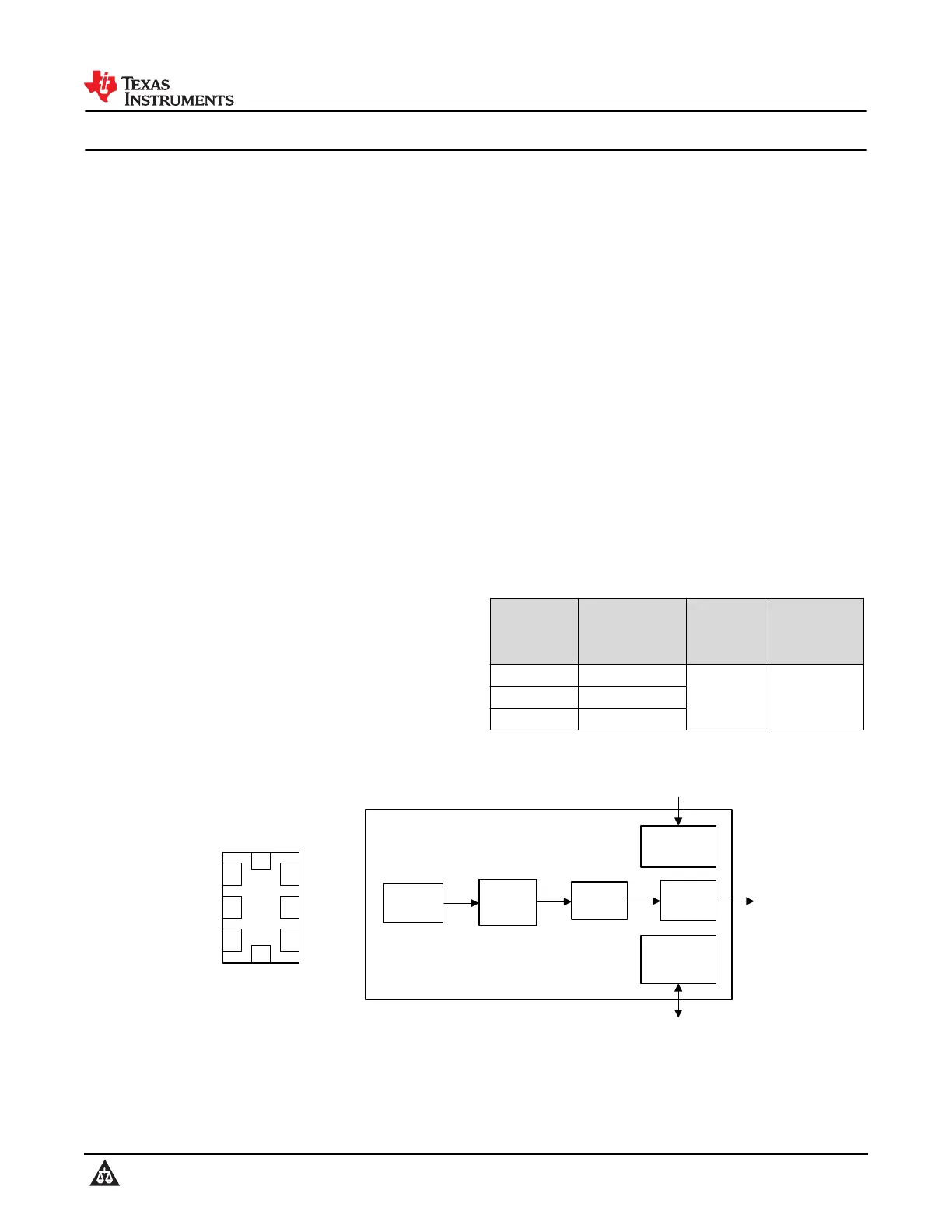

Package Information

PART

NUMBER

DEFAULT

OUTPUT FREQ

(MHz) AND

FORMAT

PACKAGE

(1)

PACKAGE

SIZE

(2)

LMK61E2156.25 LVPECL

SIA (QFM, 8)

7.00mm ×

5.00mm

LMK61E2BAA156.25 LVDS

LMK61E2BBA125 LVDS

(1)For more information, see Section 12.

(2)The package size (length × width) is a nominal value and

includes pins, where applicable.

ADDOUTN

VDDOE

GNDOUTP

SCL

SDA

16

25

43

7

8

LMK61E2

Ultra-high performance oscillator

PLL

Output

Divider

Output

Buffer

Power

Conditioning

Interface

I

2

C/EEPROM

Integrated

Oscillator

Pinout and Simplified Block Diagram

LMK61E2

SNAS674C – SEPTEMBER 2015 – REVISED MAY 2025

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Produktspezifikationen

| Marke: | Texas Instruments |

| Kategorie: | Nicht kategorisiert |

| Modell: | LMK61E2 |

Brauchst du Hilfe?

Wenn Sie Hilfe mit Texas Instruments LMK61E2 benötigen, stellen Sie unten eine Frage und andere Benutzer werden Ihnen antworten

Bedienungsanleitung Nicht kategorisiert Texas Instruments

8 März 2026

8 März 2026

8 März 2026

8 März 2026

8 März 2026

8 März 2026

8 März 2026

8 März 2026

8 März 2026

Bedienungsanleitung Nicht kategorisiert

Neueste Bedienungsanleitung für -Kategorien-

8 März 2026

8 März 2026

8 März 2026

8 März 2026

8 März 2026

8 März 2026

8 März 2026

8 März 2026

8 März 2026

7 März 2026